# perf\_events status update

Stéphane Eranian Google, Inc

CSCADS workshop Lake Tahoe, CA August 2011

#### Agenda

- Intel Sandy Bridge support

- AMD Interlagos support

- Intel offcore\_response support

- uncore PMU support

- cgroup monitoring support

- perf tool update

- libpfm4 update

#### Supported HW

- AMD64

- K8, Barcelona, Shanghai, Istanbul (Magny-Cours?)

- Fam15h: Bulldozer (core PMU)

- Fam14h: Bobcat (AMD Fusion)

- Intel X86

- P6, Core Duo/Solo, Netburst (P4)(2.6.35)

- Atom, Core, Nehalem/Westmere, SandyBridge

- any processor with architected perfmon (PMU)

- ARM

- ARMV6 (1136,1156,1176)

- ARMV7 (cortex-a8, cortex a9)

- IBM Power

- Alpha processors (EV67 and later)

#### New PMU Hardware

- Intel Sandy Bridge

- 8 generic counters (4 with HT on)

- o full width counter writes (48-bit wrmsr)

- PEBS Precise distribution (PDIR)

- PEBS Precise store

- PEBS Load Latency (LL) covers TLB and Lock

- extended OFFCORE\_RESPONSE events

- o uncore PMU

- AMD Fam15h processor (Bulldozer)\*

- o 6 core counters

- Lightweight Profiling (LWP)

- o distinct uncore PMU

- o event scheduling constraints

<sup>\*</sup> based on LKML patches posted by AMD (see http://lkml.org/lkml/2011/2/15/123)

#### Support for Intel Sandy Bridge

- support added in 2.6.39

- generic event mappings

- event scheduling

- regular PEBS (incl LBR)

- offcore\_response: limited support (2.6.39)

- PEBS-LL: patch under LKML review

- PEBS-ST: patch under LKML review

- PEBS-PDIR: partial support (2.6.39)

- uncore PMU: patch under LKML review

## Support for AMD Fam15h (Bulldozer)

- core PMU support in 2.6.39

- implements event scheduling constraints

- mapping of generic events

- No LWP support yet

- kernel xsave/xrstor patches from AMD: LKML review

- o rest of support can be encapsulated into user library

- no uncore PMU support yet

#### PEBS memory access sampling

- PEBS-LL: load latency (NHM/WSM/SNB)

- o samples location of load cache misses

- o must use event MEM TRANS RETIRED.LOADS

- o collect: instr addr, data addr, latency, data src, L2TLB, lock

- latency cycle filter (LD\_LAT MSR)

- machine state at retirement of load

- o still has off-by-1 error on instr

- PEBS-ST: precise store (SNB only)

- samples location of store misses

- must use event MEM\_TRANS\_RETIRED.STORES

- collect: instr addr, data addr, L2TLB hit, L1D hit, lock

- machine state at retirement of store

- still has off-by-1 error on instr

## PEBS memory access sampling

- proposed perf\_event abstractions (patch by Lin Ming @ Intel)

- new generic hardware events:

- PERF COUNT HW MEM LOAD

- PERF\_COUNT\_HW\_MEM\_STORE

- latency filter

- o attr->config1

- mem access infos requested via attr->sample type:

- o ld/st addr: PERF SAMPLE IP

- o data addr: PERF\_SAMPLE\_ADDR

- o latency: PERF\_SAMPLE\_LATENCY

- data src via PERF SAMPLE EXTRA:

- o abstracted: MEM\_LOAD\_L1, MEM\_LOAD\_L2, MEM\_LOAD\_LOCAL...

## perf mem proposal

#### Lin's patch adds perf mem

\$ perf mem -t load record make -i8

```

$ perf mem -t load report

Memory load operation statistics

L1-local: total latency= 28027, count= 3355(avg=8)

L2-snoop: total latency= 1430, count=

29(avg=49)

L2-local: total latency= 124, count=

8(avg=15)

4(avg=113)

L3-snoop, found M: total latency=

452, count=

L3-snoop, found no M: total latency=

0, count=

0(avg=0)

L3-snoop, no coherency actions: total latency=

18(avg=48)

875, count=

L3-miss, snoop, shared: total latency=

0(avg=0)

0, count=

L3-miss, local, exclusive: total latency=

0, count=

0(avg=0)

L3-miss, local, shared: total latency=

0. count=

0(avg=0)

L3-miss, remote, exclusive: total latency=

0, count=

0(avg=0)

L3-miss, remote, shared: total latency=

0(avg=0)

0, count=

Unknown L3: total latency=

0, count=

0(avg=0)

IO: total latency=

0, count=

0(avg=0)

Uncached: total latency= 464, count=

30(avg=15)

```

#### Intel OFFCORE\_RESPONSE event

- analyze memory traffic from core's point of view

- o can filter on type of memory request/response

- core PMU event

- programming: config + counter + filter

- filter uses extra MSR (shared when HT on in NHM/WSM)

- o filter programming: 2<sup>16</sup> combinations (NHM/WSM), 37 bits on SNB!

- perf\_events support

- must manage HT shared registers

- o must encode event + filter

- abstracted offcore events

- LKML: do not expose raw offcore, must abstract first!

- WSM/NHM: subset mapped to generic cache events

## OFFCORE\_RESPONSE (cont'd)

- LL-read-access

- offcore rsp:dmnd data rd:unc hit:other core hit snp:other core hitm

- LL-read-miss

- offcore\_rsp:dmnd\_data\_rd:io:rem\_dram:local\_dram:remote\_cache\_fwd

- LL SNB mappings missing

- documentation issues mostly

- no RAW access

- not good enough for NUMA breakdown

- o need local vs. remote traffic

- o patch proposed by Zijlstra with new generic cache events

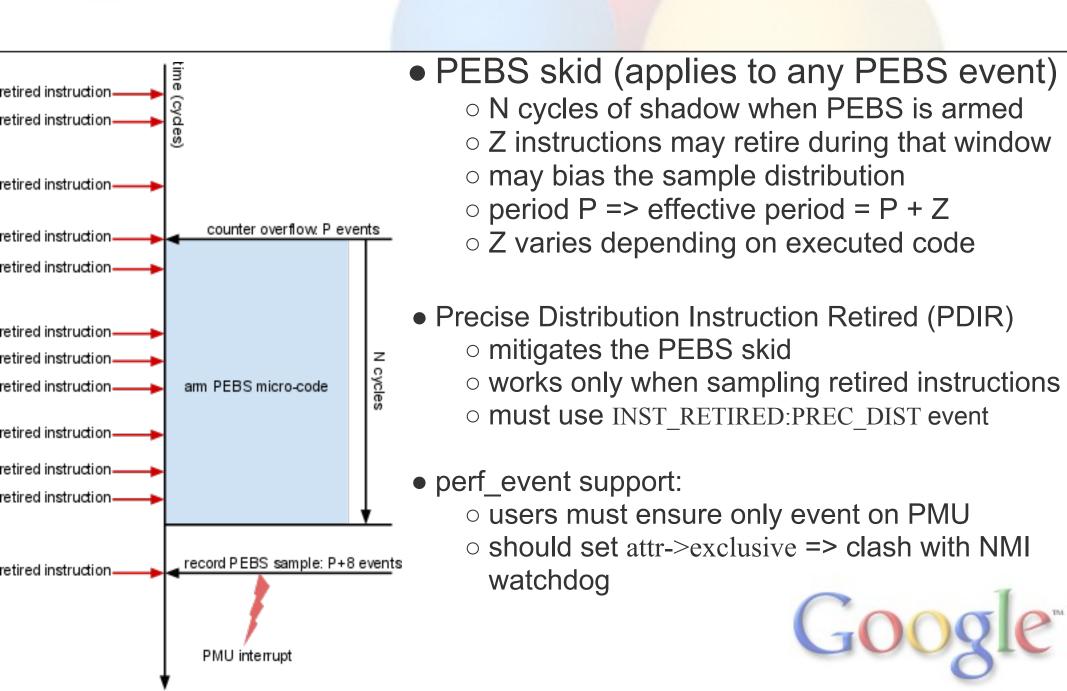

# Support for SNB PDIR sampling

#### Generic stall events

- two new generic PMU events:

- OPERF COUNT HW STALLED CYCLES FRONTEND

- PERF\_COUNT\_HW\_STALLED\_CYCLES\_BACKEND

- o no clear definitions

- LKML: definitions not needed, high correlation good enough

- counts do not have to be precise

- o but: how do you associate a cost then?

#### Multiple PMUs support

- major code restructuring in 2.6.37

- manage multiple distinct PMUs simultaneously

- events inside group must be from the same PMU

- required for uncore PMUs support

- how to identify PMU to encode event?

- o each PMU => unique id in attr->type

- o use sysfs, e.g., uncore:

/sys/bus/event\_source/devices/uncore/type /sys/bus/event\_source/devices/ibs\_op/type

- LKML: extend sysfs to expose basic event encoding

- /sys/bus/event\_source/devices/uncore/events/cycles

- o usage: perf stat -a -C 0 -e uncore: cycles

#### Intel uncore PMU support

- NHM/WSM

- 1 fixed counter (uncore clock ticks)

- 8 generic counters (44 bits)

- monitoring of very low level memory traffic

- o sample correlation to core or program impossible

- interrupt-based sampling has issues with C-states

- uncore PMU interrupt not delivered to C-sleeping cores

- o cannot lose interrupt => counter wraps around

- Lin Ming @Intel patch provides counting only

- o uses hrtimer to avoid wrap around counting issues

- raw mode access for uncore events allowed

#### Per-container monitoring

- resource container (cgroup)

- o cpuset, mem, scheduling

- can now monitor execution inside a specific cgroup:

- **ex**: perf stat -a -e cycles -G foo -- sleep 1

- extension of system-wide

- on each cpu, monitoring is active only when running a thread that belongs to the monitored cgroups

- cgroup specified via fd from cgroupfs:

- o fdc = open("/dev/cgroup/foo", O\_RDONLY)

- o fd = perf\_event\_open(&attr, fdc,0,PERF\_FLAG\_PID\_CGROUP, 0)

- upstream since 2.6.39 (contributed by Google)

#### Still missing

- taken branch sampling

- leverage LBR on Intel

- Intel NHM/WSM/SNB uncore (desktop SKUs)

- patch under review

- AMD IBS (AMD contributing)

- o patches just posted by Robert Richter @ AMD

- o patch looks very good, should get in quickly

- ability to capture machine state (regs) on interrupt

- ability to control multiplexing rate (use hrtimers)

- improved event scheduling (maximize PMU usage)

- Intel X86: unhalted\_reference\_cycles event

#### perf tool

- Curses-based GUI (NEWT toolkit)

- o not very useful

- cgroup support

- o perf stat -e cycles -G foo -a -- sleep 1

- perf report --symfs

- o point to dir with unstripped

## libpfm4

- helper library to map event names to event encoding

- libpfm4-1.0 released

- ogit repository: perfmon2.sf.net

- restructured code to support OS API attributes:

- o ex: INST\_RETIRED:period=2000000:c=1:i

- memory usage improvements

- o 37% size reduction on Intel X86 memory usage

- more HW support

- o all X86 processors, IBM Power, SPARC, ARM Cortex A8/A9

- patch for perf tool posted but still not integrated by maintainer

#### Conclusion

- improved PMU HW support in kernel

- lots of kernel patches coming to close the gaps

- perf tool still needs a lot of improvements